- MS1820

- MS1823

- MS1824

- MS1825

- MS1826

- MS1826A

- MS1826B

- MS1830

- MS1835

- MS1836S

- MS1850

- MS1851

- MS1858E

- MS1861

- MS1862

- MS2107

- MS2108

- MS2109

- MS2130

- MS2131

- MS3220

- MS7024

- MS7123

- MS7124

- MS7200

- MS7210

- MS8510

- MS9120

- MS9121

- MS9122

- MS9123

- MS9125

- MS9132

- MS9282

- MS9288A

- MS9288C

- MS9291

- MS9292

- MS9331

- MS9332

- MS9333

- MS9334

- MS9337

- MS9601A

- MS9604

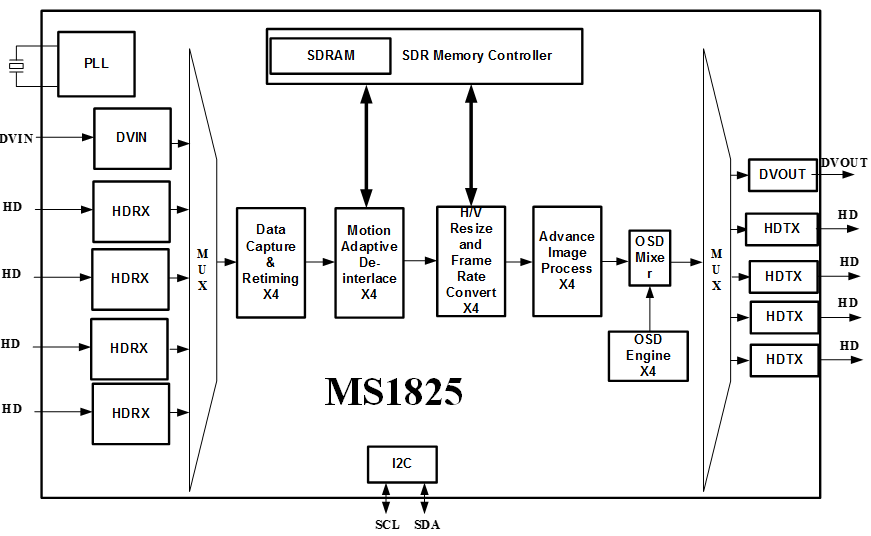

MS1825

——————————————————————————————————————————————————————————

The MS1825 is a multi-functions video processor chip. It consists of 4 independent channel HD signal inputs and 4 independent channel HD signal outputs, also includes 24 bits’ digital video input or output and 1 channel I²S & SPDIF digital audio input or output. Support 4 OSD windows with embedded font library. It can accept interlaced or progressive video input and graphic input. It has four independent video playback engines which can support PIP or POP application. Also can split one input picture into maximum four parts. In all video input & output channels, it provides a high quality display output. It is capable of advanced de-interlacing, video enhancement and frame rate conversion. OEMs can easily design a low cost and high quality system solution by MS1825’s high integration and Software support.

Features

|

4 independent channel for both input and output |

Supports 1080P HD |

|

Up to 4K@30Hz |

Supports SDR & DDR data rate |

|

Signal range: 500mV |

Supports one channel SPDIF & I²S digital audio |

|

Support extensive video format: CEA-861-F, VESA |

Independent horizontal and vertical scaling |

|

Support RGB/YCbCr444/YCbCr422 color space |

Frame rate conversion |

|

Support RGB/BT601/BT709 calorimetry |

16-bit data access |

|

Support 8/10/12/16 bits color depth |

Memory bus speed up to 188MHz |

|

Input video timing & info frame auto detection |

Support HD 1080I to 1080P conversion |

|

Embedded programmable 512 bytes (maximum) EDID |

Support SD NTSC/PAL to 480P/576P conversion |

|

Input HPD programmable & output HPD auto detection |

Edge correction de-interlace |

|

Input auto EQ |

Global noise reduction |

|

Audio sample rate from 32KHz to 192KHz |

3:2/2:2 pull-down detection |

|

Supports 24-bit RGB/YUV digital |

Brightness, saturation, contrast, HUE adjustment |

|

Supports 16-bit YUV 4:2:2 |

Embedded 1bpp font library |

|

Supports 8-bit BT656, 601 |

Four OSD window with alpha-blending |

|

Supports 8-bit BT1120 |

HLQFP216 (24mm×24mm) |

|

Supports interlace and progressive SD |

3.3V/1.2V power supply |

Function Block Diagram